What is PCB layout structure?

PCB (printed circuit board) layout structure refers to the organization and arrangement of components and interconnect copper traces on the physical board area across various design layers according to good design practices.

Proper layout structuring helps meet complex electrical connectivity needs as well as optimize manufacturability, testability and serviceability across operating lifecycles spanning years serving myriad unseen use case patterns unmodified ideally minimizing sustainability risks responsible forward.

Let’s take a deeper look at what constitutes effective PCB layout structures.

Segregation by Function

Grouping relevant circuits performing similar functions together avoids unintentional interference minimizing noise coupling simplifying architectural comprehension modularizing failure containment.

For example:

Power Supply Circuits

- Power input terminals

- Switching converters, regulators

- Bulk decoupling capacitors banks

- Fusing protecting safeguards

Microprocessor and Memory

- CPU, memory ICs clusters

- Associated bus line interfaces

- Peripheral glue logic nearby

Clock Subsystem

- Crystal reference oscillators

- Clock distribution buffers, dividers

- Sensitive clock signal traces

RF/High Speed Interfaces

- RF transceiver section

- Controlled impedance lines

- Bandpass filters

- Baluns, lightning protections

Discrete Analog Sensing

- Resistor divider sensor nodes

- Analog muxes, instrumentation amp

- EMI preventing shields maybe

Such functional clusters containment limits electrical faults propagation risks keeping system integrity resilience higher sustaining environments induced perturbations effects minimization responsibly.

Split by Board Regions

Partitioning layout further divided across physical board quadrants or grids sections allows organized allocation assignments simplifying routing completion flows phase wise in orderly staged manner.

This layout methodology segmentation includes:

A. Component Placement Regions

Group associated parts along dominant signal flows reducing path lengths critical links enabling connections completion progressions systematically reducing chaotic routing confusions minimizing complex interdependencies unresolved till final stages surprises late.

B. Power Distribution Grids

Power and ground reference planes area evenly distributed as grids ensuring uniform access across all board locations avoiding thin choke points starvation possibilities crisscross patterns interleaves.

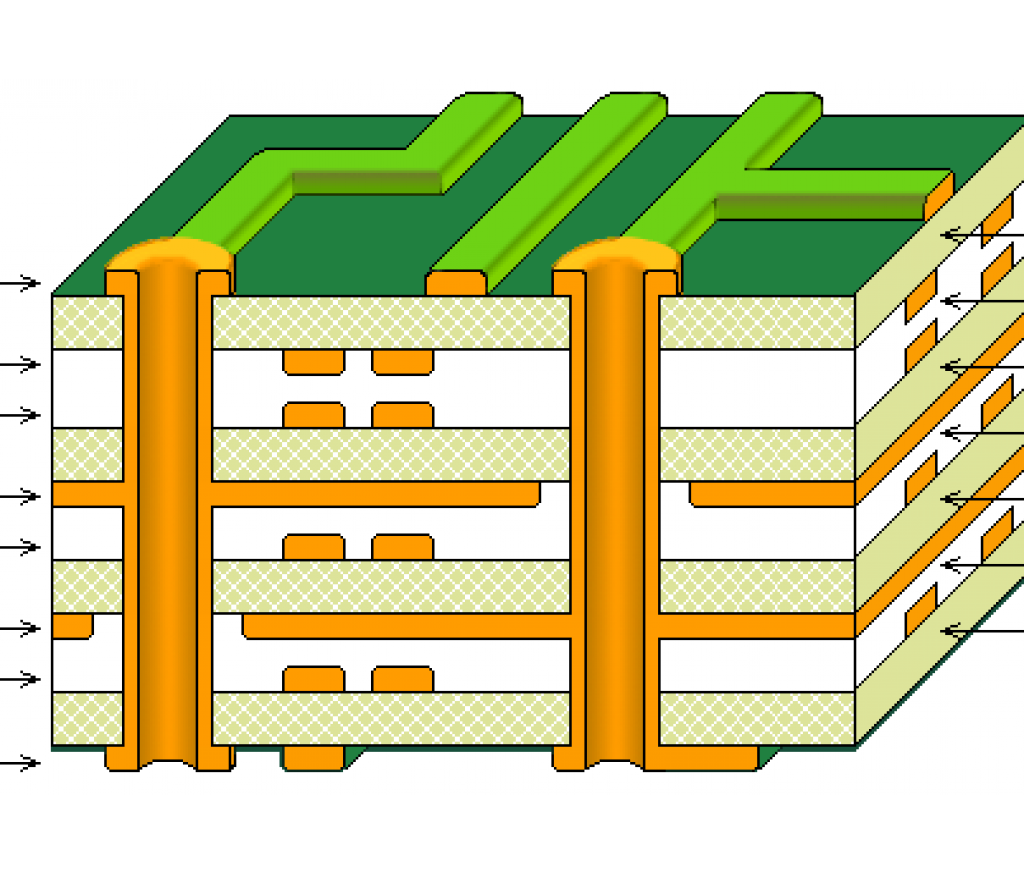

C. Signal Routing Channels

Orderly linear routing tracks and pre-placed vias arrays facilitates inter connections between various functional blocks along pre allocated intersections minimizing chaotic meandering complexities.

D. Test and Debug Features

Test points and probe access guides preservation at strategic physical locations sensing vital nodes health indications helps diagnostics ease simplicity.

Ensuring generous spacing borders between adjacent regions allows routing channels accessibility breathing room containing further density growths accommodations future sustenance needs.

Hierarchical Connectivity

Maintaining schematics source logical hierarchy reflected in layout equivalent net groupings containment enables multi-layer stack inter connections abstracted simply through connected ports logically instantiated preserving modular isolation. This minimized ripple risks boundary violations during incremental changes isolated within group avoiding systemic disturbances by ensuring change encapsulations.

For instance, key sub blocks may comprise:

A. Microcontroller

- CPU and memories sub-section

- Buffered ports breakout instances

B. Voltage Regulation

- Primary bulk conversions first

- Secondary fine grained local regulators

C. Sensor Interfaces

- Analog signal conditioning stages

- ADCs connectivity provisions

D. Application Specific Modules

- Functional algorithms electronics mapped architecture transformation from behavioral models represented hardware logic implementations

Preserving such hierarchy applying object oriented layout methodology realizes reusability productivity liberating engineers creative thoughts applications specific customization focused market differentiating aspects more.

Layout Design Guidelines

Standardizing frequently encountered guidelines as organizational templates codifies repeatability reducing reinventions optimizes reuse saving costs time productivity gains improvements sustainably allowing customization without losing structure way forward.

For example – having predefined specs on:

A. Component Packaging

- SMD parts dimensions

- Heights clearances

- Pitch spacing specs

B. Trace Routing Styles

- Single track vs bus patterns

- Line spacing basis voltage

- Line widths current capacity basis

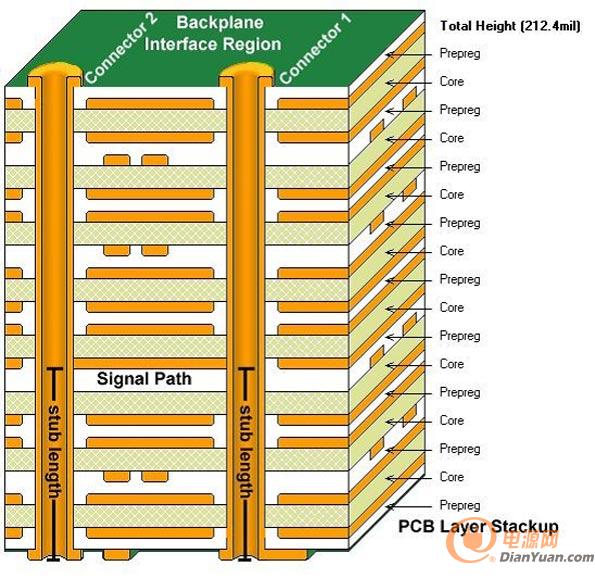

C. Via Stacking Specs

- uVia dimensions limits

- Mixed via types per layer density

- Thermal heat dissipation needs

D. Test Points Specs

- Locations reserves tracking accessibility

- Dimensions mechanical probe reliability

- Identification visual markers

Guidelines institutionalization avoids assumptions interpretations mismatch raising clarity quality.

Layout Review Checklist

Design quality validations consistency improves having established review checkpoints assessing key facets completeness satisfaction systematically avoiding escapes leaks minimizes customer returns upstream responsible sustenance achieving operational excellence journey continued zeal staying hungry wisdom humility principles withdrawal balanced pragmatism sustainably.

Let’s see some common layout review checklist points:

A. Functional

- verified schematics source connectivity match

- power sequencing supply integrity

- signal characteristics impedance match

- Team domain expertise endorsements

B. Electrical

- spacing rules adherence confirmation

- current carrying capacities heat dissipations adequacy

- transmission line terminations effectiveness

- heat sink needs identification

C. Mechanical

- enclosure form fitments

- stiffeners supports provisions

- assembly components orientations accessilibity

- test points probe access provisions

D. Manufacturing

- tolerances specifications realizable validation

- design rules checks passes confirmation

- mixed dense connectivity risks alerts identification

Institutionalizing accountability through reviews ensures quality culture adoption improving organizational maturity responsibly producing differentiating values customers over longer sustainability periods through excellence commitments demonstrating integrity priorities.

PCB Layout Structure Basics

Before adopting complex architecture advanced methodologies realizations recurrent fundamental principles act guiding beacon coherence retaining clarity must precedes sophistications chasing else risk scattered efforts drain misguided focus lacking established structured foundations sustaining ideations transformations physics successfully forward.

1. Segregate Key Domains

Keep analog circuits away from noisy digital logic, ensure radio frequency sections routed sensitively. Apply independent power domains partitioning for isolation.

2. Maintain planar symmetry

Balance placements across board quadrants, retain alignment mirroring on component locations orientation uniformly improving manufacturing processes ease optimization further.

3. Facilitate testability provisions

Accessibility considerations ensuring vital nodes observability critical links routings sensitivities predicts first silicon bring up debugging facilitation readiness confirmed apriori immune nasty surprises later.

4. Optimize serviceability

Visual identify mission critical hot swap components selective accessibility unique labelling distinguishes roles hierarchy providing easier comprehension helpers.

5. Validate design guidelines

Rules checks exercised early validates chosen specifications combinations feasibility apriori instead late stage iterations recycling avoids duplicated efforts reruns optimizing design maturity flow iteratively raising confidences qualifying manufacturing releases assessments.

6. Assess reliability risks

Application operating environments abuse cases severity identification assesses puffer zones margins adequacies indicator guiding engineering considerations predicting encapsulations needed containing exposures minimizations ahead reliability apriori.

Adhering fundamental premises minimizes unraveling downstream interdependencies surprises helping instead focus strengthening building blocks firmer simplifying learnings reapplications maximizing values deliveries sustainably responsibly.

PCB Layout Structure – FAQs

Q1. How does layout structure affect manufacturing cost?

Modular reuse based layouts reduces NREs while balancing density optimizations scale economies lowering unit costs. Also design guidelines adoption avoids unbudgeted respins lowering risks improving yields further.

Q2. How does layout affect signal quality and EMI control?

Structured power planes distribution containing return currents loop minimizes radiations while signals physical proximity placements choice relative other nodes ensures containment guard banding applied minimizes coupled interferences effectively.

Q3. How to determine components placement sequence priority?

High pin count complex ICs get locked first additionally factoring space requirements estimate reserved followed progressively next lower links dependencies down further tethered tails elements placed available areas minimize rerouting placement updates later.

Q4. How does layout structure impact system level reliability?

Prudent segregations mixed signals groups containing domains physical proximity interferences effects applied minimizes risks negative immunity influences through generously spread spacing allocations. Also selective reinforcements assessable reparability provisions predicts prolonged products lifespans usages extending responsibly.

Q5. Does layout structure affect PCB fabrication process performance?

Standardization provides reuse optimizing fabrication travels budget apriori validation avoiding surprises. Also gradual density growth provisions gives visibility planning capacities scaling matching demands maintaining continuity production committed volumes sustainability.

Conclusion

In summary, methodical printed circuit board layout structuring techniques adoption enables – judicious segregations by domains safeguarding electrical integrity, hierarchical modularity realizations simplifying connected abstractions, orderly physical groupings based streamlined placements routing completion flows, generously spread balancing provisions facilitating accessibility debuggability sustenance needs, institutionalized design guidelines integration lowering risks variability smoothing fabrication assembly optimization further gains.

Getting structures foundations right critically impacts physical designs transformations sustainably manufacturable electronics systems stablishing new competitive frontiers responsibly achieving excellence journey leapfrogs differentiating values further guiding by tenets highest quest learning ever improving raising bars continually seeking pinnacle possibilities next akin superconductors Holy Grail discoveries awe generations ahead inspiring pure creative magic manifestations brilliantly again responsibly.